## Digital Logic Design:

### A Rigorous Approach

Guy Even and Moti Medina

School of Electrical Engineering, Tel-Aviv University

Revised 5 January 2020

© Guy Even and Moti Medina 2010, 2011, 2012, 2013, 2014, 2016, 2019

This is the authors version of the book. The book shall be available for purchase from Cambridge University Press and other standard distribution channels. The reader may take one copy only for personal use. Unauthorized distribution is not allowed.

$\mathbf{2}$

### Preface

This book is an introductory textbook on the design and analysis of digital logic circuits. It has been written after 15 years of teaching hardware design courses in the school of Electrical Engineering in Tel Aviv University. The main motivation for writing a new textbook was the desire to teach hardware design rigorously. By rigorously, we mean that mathematical language and exposition is used to define the model, to specify functionality, to describe designs, to prove correctness, and to analyze cost and delay. We believe that students who study formal courses such as Algebra and Calculus can cope well with a rigorous approach. Moreover, they are likely to benefit from this approach in many ways.

The book covers the material of an introductory course in digital logic design including an introduction to Discrete Mathematics. It is self-contained, begins with basic gates and ends with the specification and implementation of simple microprocessor. The goal is to turn our students into logic designers within one semester.

The rest of this preface deals with the rational, structure, and audience of the book. We conclude with a list of the highlights some of which are new to a hardware design book.

How to acquire intuition? It is not fashionable these days to emphasize mathematical rigor. Mathematical rigor is perceived as an alienating form that dries out the passion for learning and understanding. Common teaching tactics avoid rigor (i.e., the holy definition-theorem-proof triple) and resort to examples. Since intuition is what really matters (and we of course agree with that!), in the rare cases when one feels compelled to provide a proof, the following strategy is employed. First, a long intuition precedes the proof, in an attempt to explain in advance what the proof does and why it actually works (is this part actually an apology for what is about to come?). Then, a long proof follows using partially defined terms. All we can say is that this strategy is in complete disregard of the statement: "When you have to shoot, shoot. Don't talk" [Tuco in The Good, the Bad and the Ugly].

Recall the huge endeavor of 19th century Mathematicians to formalize the calculus of real functions. Weierstrass and others undertook the task of providing a formal abstraction of the presumably well understood notions of real numbers, real functions, continuous functions, etc. We still remember our surprise when Weierstrass's function was first described to us: continuous everywhere and differentiable nowhere... The lesson is clear: intuition is gradually acquired and must be based on solid fundamentals.

What does this have to do with digital design? The quest for intuition is confronted by the fact that it is hard to formulate precise statements about objects such as digital circuits. Our approach is to give the students a solid rigorous basis for their intuition. Of course, examples are easy to follow, but might give the students the false impression that they understand the topic. We have seen many brilliant students in engineering disciplines that find it hard to acquire intuition based only on examples. Such students can easily cope with a rigorous exposition in

which delicate issues are not hidden or brushed aside.

Learn from the success of data structures and algorithms. We believe that successful teaching means that a student can implement the material from the course. After studying data structures, a student should be able to program search trees, sorting, and hashing. We believe that the same goal should be set for a logic design course. Unfortunately, most textbooks describe various circuits, provide examples for why they work, but do not train engineers who can actually design digital circuits.

The goal of this book is to bring students to a level that will enable them to understand a specification of a combinational or synchronous circuit, to design it, to prove the correctness of their design, and to be able to analyze the efficiency of the design (i.e., delay and cost).

We do not restrict this goal to isolated circuits. We show how a system is built from different circuits working in concert. In fact, we present a simple microprocessor, the design of which combines multiple modules, including: an arithmetic logic unit (with an adder, logical operators, and a comparator), a shifter, a file register (with the general purpose registers), and main memory.

The knowledge highway. Our goal is to turn our students within one semester into logic designers. To meet this goal we follow a bottom-up approach that begins with the basics and ends with a simple microprocessor. We solidify the presentation by using mathematical notations and statements and by defining the abstraction precisely. The effort spent on a formal approach pays off simply because it enables us to teach more material, in more depth, and in a shorter time. It is not surprising that towards the end of the course, students can not only design nontrivial modules, they can also identify errors in designs and suggest ways to correct these errors.

**Our teachers.** When writing this book, the first author and, by transitivity, the second author were mainly influenced by three people: Shimon Even, Ami Litman, and Wolfgang Paul.

It was Shimon Even who stated that: (1) Never complain or be surprised by the students lack of knowledge - just teach it! (2) Digital design is the same art as algorithm design. The only difference is the model of computation. (3) Identify the methods and be systematic. In other words, turn digital design into a discipline.

It was Ami Litman who demanded: (1) Always verify that your abstraction makes sense. Don't hesitate to refute the model by introducing absurd consequences. (2) Introduce a design by a sequence of evolutionary modifications starting with a simple straightforward yet costly design and ending with an evolved yet efficient design. Each modification preserves functionality, and hence, the final design is correct. Describe each modification as a general transformation that can be applied in a wide variety of settings. (3) Focus on large instances. Optimization of small instances depends on the technology and is not likely to reveal insights.

Wolfgang Paul's rules are: (1) Formulate a precise specification and prove that the design satisfies the specification. (2) Write the equations that describe the delay and cost. Solving these equations asymptotically is nice, but from a practical point of view, it suffices to solve them numerically for the sizes one needs to actually design. (3) Keep in mind that the goal is to design a correct well understood system. Avoid fancy optimizations that eventually impede this goal. This rule applies both for teaching and for actual design. **Our Students.** Our students are Electrical Engineering undergraduate students in their second or third semester. The students lack background in discrete mathematics, and the first part of the book deals with filling this gap. This is considered the easy part of the course.

Following the logic design course, our students take courses on devices (both analog and digital). Students who choose the computers' track also study computer organization, computer architecture, and practice digital design in a lab with an FPGA platform. In this lab they implement the simplified DLX microprocessor described in Part IV of the book. This implementation is from basic gates (e.g., no library modules such as adders are used). In the end of the lab, the students program a nontrivial program in assembly language and execute it on their design.

Apart from training the students in logic design, we also teach discrete methods that are used in data structures and algorithms. In particular, we focus on induction and recursion, trees and graphs, and recurrence equations.

**Structure of the book.** The book consists of four parts: (I) Preliminaries, (II) Combinational Circuits, (III) Synchronous Circuits, and (IV) A Simplified DLX.

The first part of the book is a short introduction to discrete mathematics. We made an effort to include only topics in discrete math that are actually used in the other parts. This is considered the easy part of the course, however, it is essential for students that lack background in discrete mathematics. In addition, this part helps students get used to working with definitions, mathematical notation, and proofs.

The second part of the book is the heart of the book. It focuses on Boolean functions and on methods for building circuits that compute Boolean functions. We begin by representation by Boolean formulas, e.g., sum of products and product of sums. This establishes the connection between Boolean functions and propositional logic. We then define combinational gates and combinational circuits and define two quality measures: cost and propagation delay.

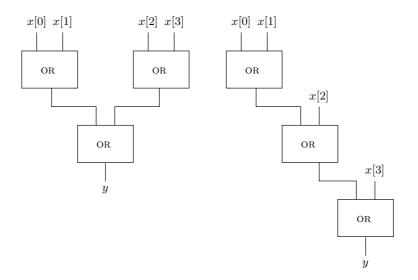

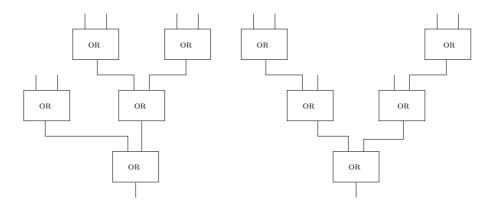

The study of combinational circuits begins with circuits that have a topology of a tree. At this point we introduce lower bounds on the number of gates and the propagation delay of a combinational circuit that implements a Boolean function such as the OR of n bits. Logical simulation is presented in an algorithmic fashion using topological ordering of a directed acyclic graph. The same approach is used for computing the propagation delay of combinational circuit.

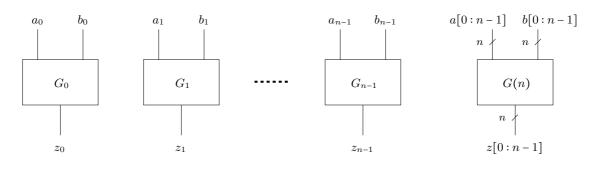

We proceed with a variety of combinational circuits (e.g., decoders, encoders, selectors, shifters, and adders). Designs are presented in a parametric fashion, where the parameter is the length of the input. Whenever possible, designs are recursive and proofs are by induction.

Chapter 10 in the second part explains the digital abstraction. The purpose of this chapter is to build a bridge between the analog world and the digital world.

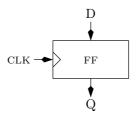

Synchronous circuits are studied in the third part of the book. We first introduce the clock signal and edge triggered D-flip-flops. Only one type of flip-flop is discussed in detail. This discussion explains the different timing parameters of a flip-flop including an explanation of why so many parameters are required. Other types of flip-flops are considered as finite state machines with two states and are implemented using a D-flip-flop and additional combinational logic. Synchronous circuits are viewed in two ways: (1) Memory modules, such as: registers, random access memory (RAM), and read-only memory (ROM), and (2) Finite state machines, including their analysis and synthesis.

Algorithmic issues related to synchronous circuits include logical simulation and calculation of the minimum clock period. These algorithms are presented via reductions to combinational circuits. Students who have studied the first three parts of the book should have a good idea of what computer aided design tools for designing digital circuits do.

The last part of the book deals with the design of a simple microprocessor. Connections are made between the machine language, assembly, high level programming, the instruction set architecture (ISA). We present an implementation of the simple microprocessor using the modules from Parts II and III. The design methodology is to present the simplest microprocessor implementation that supports the ISA. We present an unpipelined multi-cycle microprocessor based on a simple datapath and a small finite state machine.

How to use this book? This book is written as a textbook for an introductory course in digital design to undergraduate students in Electrical Engineering and Computer Science. The following material is considered advanced, and may be omitted: (i) Section 5.6: More on Unique Binary Representation, (ii) Chapter 8: Computer Stories: Big Endian vs. Little Endian, (iii) Section 9.6: Minimization Heuristics, (iv) Chapter 10: The Digital Abstraction, (v) Sections 17.3-17.5. Advanced material as well as advanced questions and examples are marked with an asterisk \*.

When we teach this course, we spend roughly five weeks on Part I, five weeks on Part II, and five weeks on Parts III and IV.

We suggest to start the course very rigorously and gradually relax rigor when repeating a proof technique that was used before.

Logic design, like swimming, cannot be taught without immersion. We therefore include homework assignments in which students practice logic design using a schematic entry tool and a logic simulator. We found the open source Logisim software both easy to use and powerful enough for our purposes.

We also use a DLX assembly simulator so that students can practice assembly programing of constructs in high level programming (e.g., if-then-else statements, loops, arrays, etc.).

**Highlights.** We list the main highlights of the book.

- 1. *The book is self-contained.* We do not assume the students have any prior knowledge of discrete math, propositional logic, asymptotics, graphs, hardware, electronics, etc.

- 2. A complete teaching tool. In each chapter, we tried to make a clear separation between (i) conceptual parts containing new materials, (ii) applications and examples that are based on this new material, and (iii) problems. There are many benefits to this approach both for the teacher and the student. One clear advantage is that the examples can be covered in greater detail during recitations.

- 3. "Nothing is hidden". We adhere to the rule that all the details are complete, and every claim is proven.

- 4. *Methodology as a "ritual*". Each design is presented in four steps: specification, design, correctness proof, and analysis of delay and cost. The specification formally defines what a circuit should do. Without a formal specification, it is impossible to prove correctness. Most designs are described using recursion, and correctness is usually proved using induction. Finally, analysis of cost and delay is carried out by formulating recurrence equations and solving them.

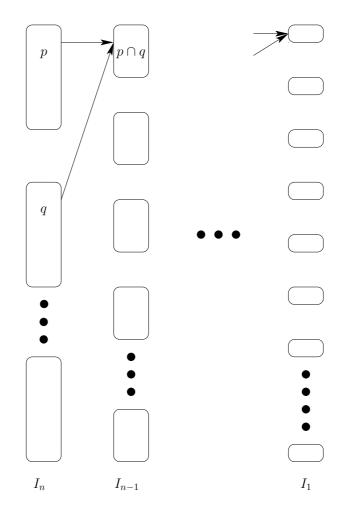

- 5. The recursion-induction pair. Instead of designing circuits for specific input lengths, we consider the task of designing circuits with a parameter n specifying the length of the inputs. For example, we consider addition of n-bit numbers, n:1-selectors, etc. These designs are described recursively. The first advantage is that we present a precise and formal definition of the design for any input length. The second advantage is that we prove the correctness of the design for any input length. Naturally, the proof is carried out using induction.

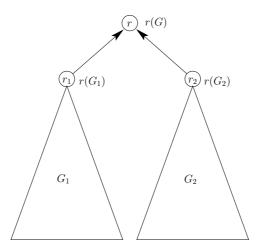

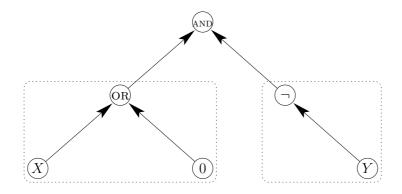

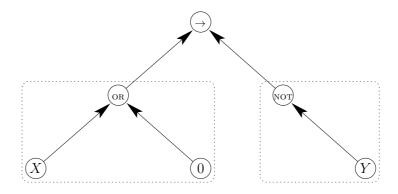

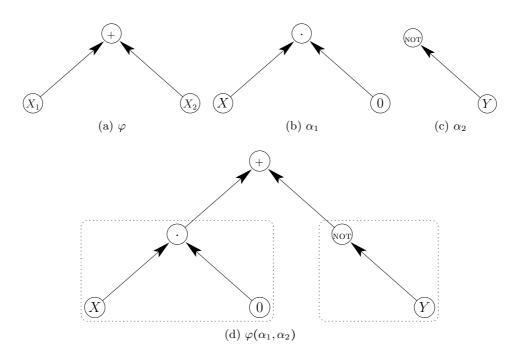

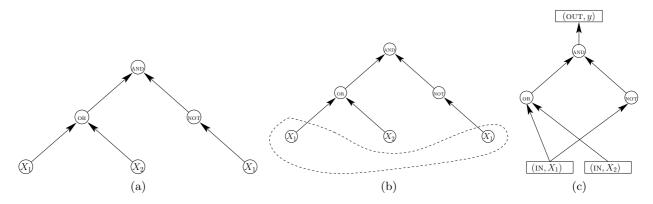

- 6. *Modeling circuits as graphs.* We use the language of graphs to describe formulas and circuits. Boolean formulas are defined by parse trees. Circuits are defined using directed graphs. This approach enables us to present a clean and precise definition of propagation delay and minimum clock period using longest paths in a directed graph. With a small effort, it is possible to extend this approach also to the more elaborate setting of nonuniform delays between input and output ports of gates.

- 7. Lower bounds. We prove simple lower bounds on the cost and the delay of a combinational circuit that implement Boolean functions. The ability to formally state that a design is an optimal adder design is remarkably powerful. Our lower bounds are stated in terms of the number of inputs that an output depends on (i.e., the "cone" of an output). These lower bounds are easy to apply to all the Boolean functions that are discussed.

- 8. *Algorithmic approach.* Tasks such as logical simulation, computation of propagation delay, and minimum clock period are presented as algorithmic problems. Algorithms are presented for solving these problems, and the correctness of these algorithms is proven.

For example, the algorithmic approach is used to teach timing analysis as follows: we present an algorithm, prove its correctness, and run it on an example. In this fashion, the topic of timing analysis is described in a precise and concise fashion that does not require lengthy examples. One may ask why not teach about timing analysis with different delays for different transitions (i.e., the time required for transition of the output from zero to one does not equal the time required for the transition from one to zero). Indeed, this question pertains to the lasting argument about the usefulness of worst case analysis. We resort to worst case timing analysis simply because it is intractable to decide whether the output of a combinational circuit ever equals one (see Section 9.5).

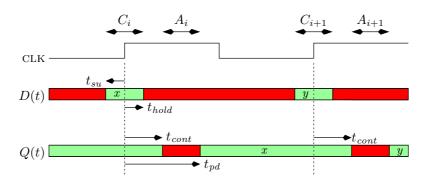

- 9. Relations to analog world. In Chapters 10 and 17 we connect the physical analog world to the digital abstraction. Two physical phenomena are discussed in detail: noise and metastability. We show how noise is overcome by using different threshold for inputs and outputs. We show how metastability is mitigated using the timing parameters of a flip-flop (i.e., setup time, hold time, contamination delay, and propagation delay). We explicitly mention issues that can not be resolved within the digital abstraction (e.g., reset controller).

- 10. Zero propagation delay as functional model. In Chapter 18 on memory modules we introduce the zero delay model. In the zero delay model transitions of all signals are instantaneous. This means that the flip-flop's output at a certain cycle equals the value of the input sampled during the previous cycle. This simplified discrete timing model is used for specifying and simulating the functionality of circuits with flip-flops. The advantage of this approach is that it decouples the issues of functionality and timing into two separate issues.

**Karnaugh Maps.** A quick comparison of this book with other books on Logic Design will reveal that we mention Karnaugh maps [7] only very briefly in Section 9.6.6. There is a good reason for this brief mentioning.

Karnaugh maps are a technique for finding the minimum number of products in a sum-ofproducts representation of a Boolean function. The input to the technique of Karnaugh maps is the truth table of the Boolean function. Thus, the input to this technique is exponential in the number of variables, and therefore cannot be considered efficient. In addition, the maps are actually two-dimensional tables, and are convenient to use for at most four variables. Experts, of course, are proud that they can use this technique also for five and even six variables! Given that the technique of Karnaugh maps has an exponential running time and is limited to few variables, we do not think it is an important issue in Logic Design. One should bear in mind, that the difference between a reasonable representation and the best representation for a function over six variables is constant. Moreover, with such small functions, even exhaustive search makes sense if one is really interested in finding the "best" representation.

Teachers insisting on teaching heuristics for finding the minimum number of products in a sum-of-products representation of a Boolean function can teach the Quine-McCluskey heuristic [15, 16, 11]. Our presentation of the Quine-McCluskey heuristic uses a layered graph over the implicants instead of a tabular approach. We hope that this choice favors notions over notation. Unfortunately, the full details of the heuristic require almost 10 pages. We therefore marked this section by an asterisk.

**Recurrence Equations.** We use recurrences to describe the cost and delay of circuits defined recursively. We do not introduce the "master theorem" for solving recurrences. The reason is that we find this theorem to be too general for the students at this stage (they do learn it later in the algorithms course). Instead, we resort to solving the specific recurrences we encounter later in the book.

**References.** There are many books on Discrete Mathematics. Two Discrete Math books that also treat Boolean Algebra and Logic Design are by McEliece et. al [12] and Mattson [10].

There are many books on Logic Design and Computer Structure. We were mainly influenced by the book of Mueller and Paul [13] in the choice of combinational circuits and the description of the processor. We use the simplified timing diagrams from the notes of Litman [9]. These notes also helped with the description of the digital abstraction and flip-flops. The book by Ward and Halstead [18] describes, among other things, the problem of meta-stability, arbitration, and the abstraction provided by an instruction set architecture. The book by Ercegovac et. al [3] uses a hardware description language to design circuits. The book by Ercegovac and Lang [2] deals with computer arithmetic.

Most textbooks do not introduce Boolean formulas via parse trees. In the book by Howson [6] propositional logic is described by trees.

More material on finite automata (a.k.a. finite state machines) appears in the book by Hopcroft and Ullman [5]. The book by Savage [17] starts with basic hardware and ends with advanced material in computability.

The DLX processor architecture was designed by John L. Hennessy and David A. Patterson [14] as an educational architecture that demonstrates the principles of a RISC processor without the elaborate details of a commercial processor. Our simplified DLX architecture is based on it and on the simplified architecture designed in the RESA lab in Wolfgang Paul's group in the University of the Saarland. See also the book by Mueller and Paul [13] for a concise description of the DLX architecture and its implementation.

Book Homepage. The homepage of the book is:

http://www.eng.tau.ac.il/~guy/Even-Medina/

We plan to maintain this homepage so that it contains the following:

- Authors version of the book in PDF format.

- Slides that we use for the teaching.

- Errata and a simple form for reporting errors.

- Links to simulators (Logisim and a DLX assembly simulator).

- Supplementary material.

Finally, we would like to thank the anonymous reviewers. Reports of mistakes (all of which are solely our fault) would be greatly appreciated.

Guy Even and Moti Medina Tel Aviv, March 2012

PREFACE

## Contents

| $\mathbf{P}_{\mathbf{I}}$ | refac          | e                                             | i         |

|---------------------------|----------------|-----------------------------------------------|-----------|

| Ι                         | Pre            | eliminaries                                   | 1         |

| 1                         | Set            | s and Functions                               | 3         |

|                           | 1.1            | Sets                                          | 3         |

|                           | 1.2            | Relations and Functions                       | 10        |

|                           | 1.3            | Boolean Functions                             | 14        |

|                           |                | 1.3.1 Truth Tables                            | 14        |

|                           | 1.4            | Commutative and Associative Binary Operations | 16        |

| <b>2</b>                  | Ind            | uction and Recursion                          | <b>21</b> |

|                           | 2.1            | Induction                                     | 21        |

|                           | 2.2            | Recursion                                     | 25        |

|                           | 2.3            | Application: One-to-one and Onto Functions    | 26        |

| 3                         | $\mathbf{Seq}$ | uences and Series                             | <b>31</b> |

|                           | 3.1            | Sequences                                     | 31        |

|                           | 3.2            | Series                                        | 33        |

| 4                         | Dir            | ected Graphs                                  | 41        |

|                           | 4.1            | Definitions                                   | 41        |

|                           | 4.2            | Topological Ordering                          | 45        |

|                           | 4.3            | Longest path in a DAG                         | 46        |

|                           | 4.4            | Rooted Trees                                  | 50        |

| <b>5</b>                  | Bin            | ary Representation                            | 57        |

|                           | 5.1            | Division and Modulo                           | 57        |

|                           | 5.2            | Bits and Strings                              | 58        |

|                           | 5.3            | Bit Ordering                                  | 59        |

|                           | 5.4            | Binary Representation                         | 60        |

|                           | 5.5            | Computing a Binary Representation             | 62        |

|                           | 5.6            | More on Unique Binary Representation*         | 69        |

| CO | NT  | E            | NΤ | S             |

|----|-----|--------------|----|---------------|

|    | 111 | . <b>Ľ</b> 4 | ۷I | $\mathcal{O}$ |

| 6  | Pro  | positional Logic 7                                             | 3            |

|----|------|----------------------------------------------------------------|--------------|

|    | 6.1  | Boolean Formulas                                               | 3            |

|    | 6.2  | Truth Assignments                                              | 8            |

|    | 6.3  | Satisfiability and Logical Equivalence                         | 1            |

|    | 6.4  | Interpreting a Boolean Formula as a Function                   | <b>2</b>     |

|    | 6.5  | Substitution                                                   | 6            |

|    | 6.6  | Complete Sets of Connectives                                   | 9            |

|    | 6.7  | Important Tautologies                                          | 2            |

|    | 6.8  | De Morgan's Laws                                               |              |

|    |      | 6.8.1 Negation Normal Form                                     | 5            |

| 7  | Asv  | mptotics 10                                                    | 1            |

| •  | 7.1  | Order of Growth Rates                                          |              |

|    | 7.2  | Recurrence Equations                                           |              |

|    |      |                                                                | Ŭ            |

| 8  | Con  | nputer Stories: Big Endian vs. Little Endian <sup>*</sup> 11   | 3            |

|    |      |                                                                |              |

| II | Co   | ombinational Circuits 11                                       | 5            |

| 9  | Rep  | resentation by Formulas 11                                     |              |

|    | 9.1  | Sum of Products                                                | 8            |

|    | 9.2  | Product of Sums                                                |              |

|    | 9.3  | The Finite Field $GF(2)$                                       |              |

|    |      | 9.3.1 Polynomials over $GF(2)$                                 |              |

|    | 9.4  | Satisfiability                                                 |              |

|    | 9.5  | Relation to P vs. NP                                           |              |

|    | 9.6  | Minimization Heuristics <sup>*</sup>                           |              |

|    |      | 9.6.1 Basic Terminology and Properties                         |              |

|    |      | 9.6.2 The Implicants' Graph                                    |              |

|    |      | 9.6.3 Essential Prime Implicants                               |              |

|    |      | 9.6.4 Optimality Conditions                                    |              |

|    |      | 9.6.5The Quine-McCluskey Heuristic139.6.6Karnaugh Maps13       |              |

|    |      | 9.0.0 Karnaugh Maps                                            | 1            |

| 10 |      | Digital Abstraction* 14                                        | _            |

|    |      | Transistors                                                    |              |

|    |      | A CMOS inverter                                                |              |

|    |      | From analog signals to digital signals                         |              |

|    |      | Transfer functions of gates                                    |              |

|    |      | The bounded-noise model                                        |              |

|    | 10.6 | The digital abstraction in presence of noise                   |              |

|    |      | 10.6.1 Input and output signals                                |              |

|    | 10 7 | 10.6.2 Redefining the digital interpretation of analog signals |              |

|    |      | Stable signals                                                 |              |

|    | 10.8 | Summary                                                        | $\mathbf{Z}$ |

### CONTENTS

| 11 | Four  | ndatio                                                    | ons of combinational circuits                                                 |            | 153                     |

|----|-------|-----------------------------------------------------------|-------------------------------------------------------------------------------|------------|-------------------------|

|    | 11.1  | Combi                                                     | inational gates - an analog approach                                          | • •        | . 154                   |

|    | 11.2  | Back t                                                    | to the digital world                                                          |            | . 155                   |

|    |       | 11.2.1                                                    | Example                                                                       |            | . 157                   |

|    | 11.3  | Combi                                                     | inational gates                                                               |            | . 158                   |

|    | 11.4  | Wires                                                     | and Nets                                                                      |            | . 158                   |

|    | 11.5  | Combi                                                     | inational circuits                                                            |            | . 160                   |

|    | 11.6  | Proper                                                    | rties of Combinational Circuits                                               |            | . 163                   |

|    | 11.7  | Simula                                                    | ation and Delay Analysis                                                      |            | . 165                   |

|    | 11.8  | Compl                                                     | leteness                                                                      |            | . 169                   |

|    | 11.9  | Cost a                                                    | and propagation delay                                                         |            | . 173                   |

|    | 11.1( | )Examp                                                    | ple: relative gate costs and delay                                            |            | . 173                   |

|    |       | -                                                         | ntics and Syntax                                                              |            |                         |

|    | 11.12 | 2Summ                                                     | nary                                                                          |            | . 174                   |

|    |       |                                                           |                                                                               |            |                         |

| 12 | Tree  |                                                           |                                                                               |            | 177                     |

|    |       |                                                           | iative Boolean Functions                                                      |            |                         |

|    | 12.2  |                                                           | of Associative Boolean Gates                                                  |            |                         |

|    |       |                                                           | Relation to Boolean Formulas                                                  |            |                         |

|    |       |                                                           | Cost Analysis                                                                 |            |                         |

|    |       |                                                           | Delay Analysis                                                                |            |                         |

|    | 12.3  | -                                                         | nality of Trees                                                               |            |                         |

|    |       |                                                           | Definitions                                                                   |            |                         |

|    |       |                                                           | Graphical Properties of Implementations of Functions                          |            |                         |

|    |       |                                                           | Lower Bound on Cost                                                           |            |                         |

|    |       |                                                           | Lower Bound on Delay                                                          |            |                         |

|    | 12.4  | Summ                                                      | nary                                                                          |            | . 191                   |

| 13 | Dec   | oders a                                                   | and Encoders                                                                  |            | 193                     |

| 10 |       |                                                           | · · · · · · · · · · · · · · · · · · ·                                         |            |                         |

|    |       |                                                           | lers                                                                          |            |                         |

|    |       |                                                           | Division in Binary Representation                                             |            |                         |

|    |       |                                                           | Definition of Decoder                                                         |            |                         |

|    |       |                                                           | Brute force design                                                            |            |                         |

|    |       |                                                           | An optimal decoder design                                                     |            |                         |

|    |       |                                                           | Correctness                                                                   |            |                         |

|    |       |                                                           | Cost and delay analysis                                                       |            |                         |

|    |       |                                                           | Asymptotic Optimality                                                         |            |                         |

|    | 13.3  |                                                           | lers                                                                          |            |                         |

|    |       |                                                           | Hamming Distance and Weight                                                   |            |                         |

|    |       |                                                           | Concatenation of Strings                                                      |            |                         |

|    |       |                                                           |                                                                               |            |                         |

|    |       |                                                           | 0                                                                             |            | 202                     |

|    |       |                                                           | Definition of Encoder                                                         |            |                         |

|    |       | 13.3.4                                                    | Definition of Encoder       Brute Force Implementation                        |            | . 203                   |

|    |       | $13.3.4 \\ 13.3.5$                                        | Definition of EncoderBrute Force ImplementationImplementation and Correctness | · ·        | . 203<br>. 204          |

|    |       | $\begin{array}{c} 13.3.4 \\ 13.3.5 \\ 13.3.6 \end{array}$ | Definition of Encoder       Brute Force Implementation                        | · ·<br>· · | . 203<br>. 204<br>. 205 |

| CONTENTS |

|----------|

|----------|

|    |      | 13.3.9 Asymptotic Optimality                                                | 07 |

|----|------|-----------------------------------------------------------------------------|----|

|    | 13.4 | Summary                                                                     |    |

|    |      |                                                                             |    |

| 14 |      | ctors and Shifters 21                                                       |    |

|    | 14.1 | Multiplexers   21                                                           |    |

|    | 14.0 | 14.1.1 Implementation                                                       |    |

|    | 14.2 | Cyclic Shifters                                                             |    |

|    |      | 14.2.1 Implementation                                                       |    |

|    | 149  | 14.2.2 Correctness and analysis of cost and delay                           |    |

|    | 14.3 | Logical Shifters                                                            |    |

|    |      | 14.3.1 Implementation                                                       |    |

|    | 144  | 14.3.2 Reduction of right shift to left shift                               |    |

|    | 14.4 | Arithmetic Shifters                                                         |    |

|    |      | 14.4.1 Two's complement       22         14.4.2 Arithmetic shifter       22 |    |

|    | 145  |                                                                             |    |

|    | 14.5 | Summary                                                                     | 20 |

| 15 | Add  | lition 22                                                                   | 29 |

|    |      | Definition of a binary adder                                                |    |

|    |      | Ripple Carry Adder                                                          |    |

|    |      | 15.2.1 Correctness proof                                                    |    |

|    |      | 15.2.2 Delay and cost analysis                                              |    |

|    | 15.3 | Lower Bounds                                                                |    |

|    |      | 15.3.1 Carry bits                                                           | 33 |

|    |      | 15.3.2 Cone of adder outputs                                                | 33 |

|    |      | 15.3.3 Lower bounds                                                         | 34 |

|    | 15.4 | Conditional Sum Adder                                                       | 34 |

|    |      | 15.4.1 Motivation                                                           | 34 |

|    |      | 15.4.2 Implementation                                                       | 35 |

|    |      | 15.4.3 Delay and cost analysis                                              | 36 |

|    | 15.5 | Compound Adder                                                              | 36 |

|    |      | 15.5.1 Implementation                                                       | 37 |

|    |      | 15.5.2 Correctness                                                          | 37 |

|    |      | 15.5.3 Delay and cost analysis                                              | 38 |

|    | 15.6 | Reductions between sum and carry bits                                       | 39 |

|    | 15.7 | Redundant and non-redundant representation                                  | 39 |

|    | 15.8 | Summary                                                                     | 40 |

|    | ~.   |                                                                             |    |

| 16 |      | and Addition 24                                                             |    |

|    |      | Representation of negative integers                                         |    |

|    |      | Computing a two's complement representation                                 |    |

|    |      | Negation in two's complement representation                                 |    |

|    |      | Properties of two's complement representation                               |    |

|    | 16.5 | Reduction: two's complement addition to binary addition                     |    |

|    |      | 16.5.1 Detecting overflow                                                   |    |

|    | 10.0 | 16.5.2 Determining the sign of the sum                                      |    |

|    | 10.0 | A two's-complement adder                                                    | აპ |

| 16.7 | A two's complement adder/subtractor $% \mathcal{A}$ |  |  | • |       | <br>• |  | • |   | • | • |   |   | . 2 | 254 |

|------|-----------------------------------------------------|--|--|---|-------|-------|--|---|---|---|---|---|---|-----|-----|

| 16.8 | Summary                                             |  |  | • | <br>• | <br>• |  | • | • | • | • | • | • | . 2 | 255 |

### III Synchronous Circuits

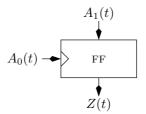

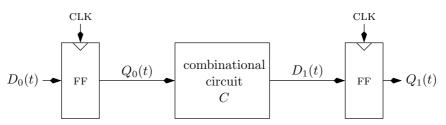

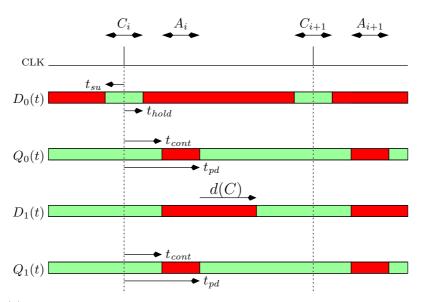

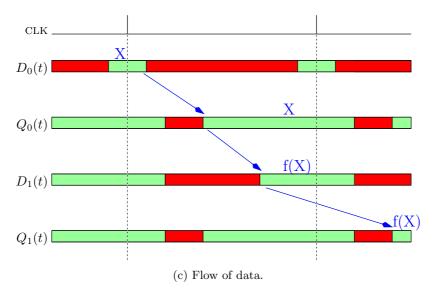

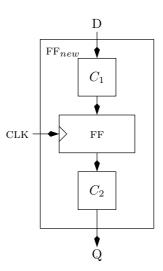

| 17 | Flip | -Flops                                                  | 261 |

|----|------|---------------------------------------------------------|-----|

|    | 17.1 | The clock                                               | 262 |

|    | 17.2 | Edge-triggered Flip-Flop                                | 264 |

|    | 17.3 | Arbitration <sup>*</sup>                                | 265 |

|    | 17.4 | Arbiters - an impossibility result <sup>*</sup>         | 266 |

|    | 17.5 | Necessity of critical segments <sup>*</sup>             | 268 |

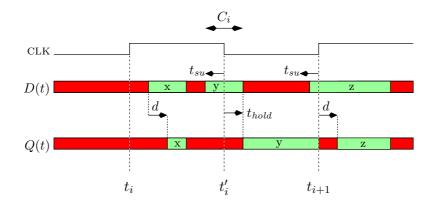

|    | 17.6 | A Timing Example                                        | 270 |

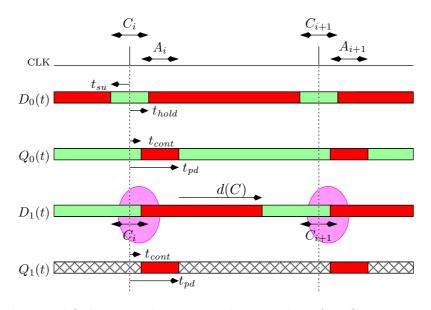

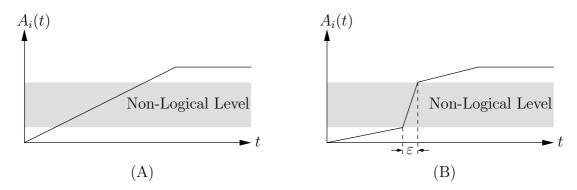

|    |      | 17.6.1 Non-empty intersection of $C_i$ and $A_i$        | 270 |

|    | 17.7 | Bounding Instability                                    | 272 |

|    | 17.8 | Other types of memory devices                           | 274 |

|    |      | 17.8.1 D-Latch                                          | 274 |

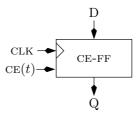

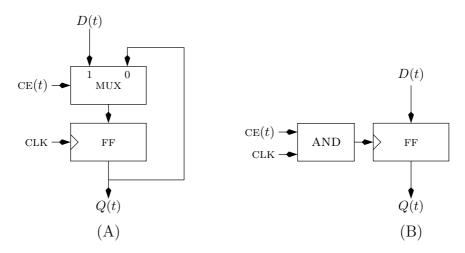

|    |      | 17.8.2 Clock enabled flip-flops                         | 275 |

|    | 17.9 | Summary                                                 | 276 |

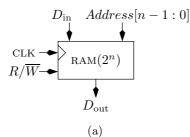

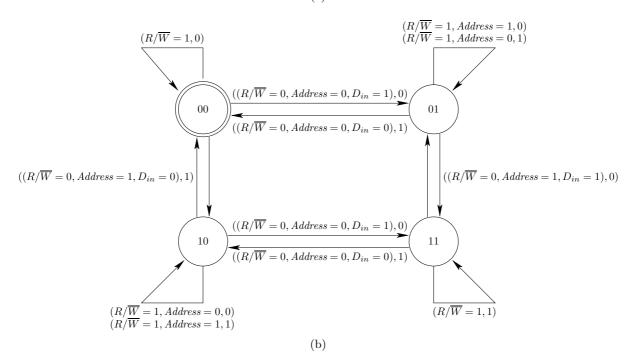

| 18 | Mer  | nory Modules                                            | 279 |

|    |      | The Zero Delay Model                                    | 280 |

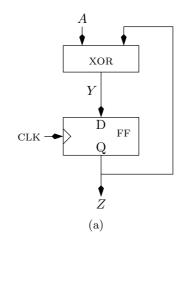

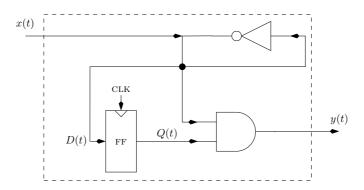

|    |      | 18.1.1 Example: Sequential XOR                          |     |

|    | 18.2 | Registers                                               |     |

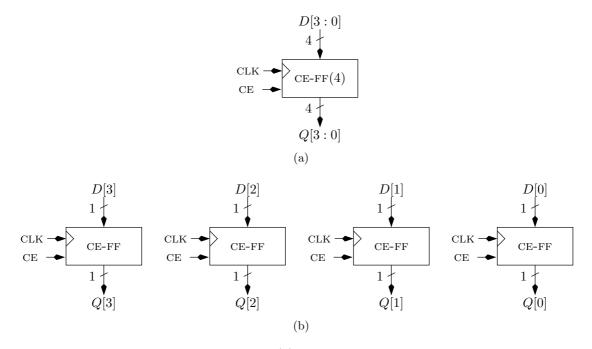

|    |      | 18.2.1 Parallel Load Register                           |     |

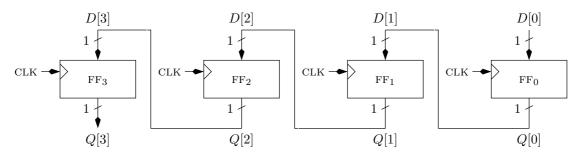

|    |      | 18.2.2 Shift Register                                   |     |

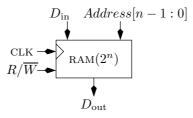

|    | 18.3 | Random Access Memory (RAM)                              |     |

|    |      | 18.3.1 A simple Implementation of a RAM                 |     |

|    | 18.4 | Read-Only Memory (ROM)                                  |     |

|    |      | Summary                                                 |     |

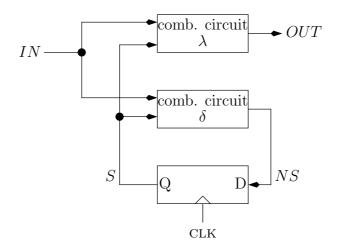

| 19 | Fom  | ndations of Synchronous Circuits                        | 289 |

|    |      | Definition                                              |     |

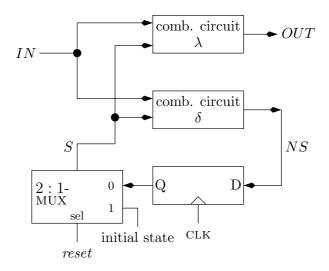

|    |      | The Canonic Form of a Synchronous Circuit               |     |

|    |      | Timing Analysis: the canonic form                       |     |

|    | 10.0 | 19.3.1 An Easy Example                                  |     |

|    |      | 19.3.2 Input/Output Timing Constraints                  |     |

|    |      | 19.3.3 Sufficient Conditions                            |     |

|    |      | 19.3.4 Satisfying the Timing Constrains                 |     |

|    |      | 19.3.5 Initialization                                   |     |

|    | 19.4 | Functionality: the canonic form                         |     |

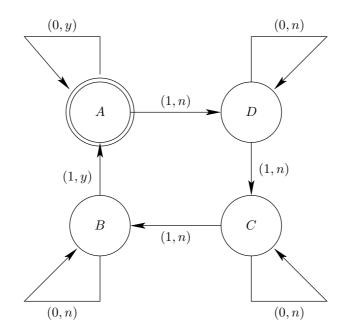

|    |      | Finite State Machines                                   |     |

|    |      | Timing analysis: the general case                       |     |

|    | -    | 19.6.1 Timing Constraints                               |     |

|    |      | 19.6.2 Algorithms: feasibility and minimum clock period |     |

|    |      | 19.6.3 Algorithms: correctness                          |     |

|    | 19.7 | Simulation of Synchronous Circuits                      |     |

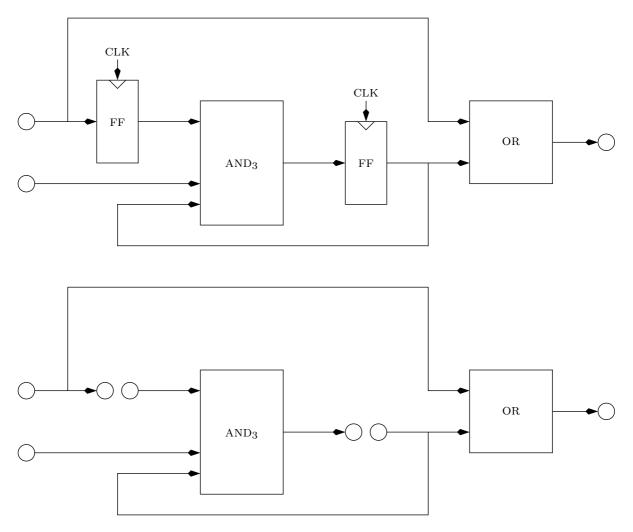

|    |      | Synthesis and Analysis                                  |     |

259

#### CONTENTS

|    |       | 19.8.1 Analysis                              |

|----|-------|----------------------------------------------|

|    |       | 19.8.2 Synthesis                             |

|    | 19.9  | Summary                                      |

|    | 19.10 | Problems                                     |

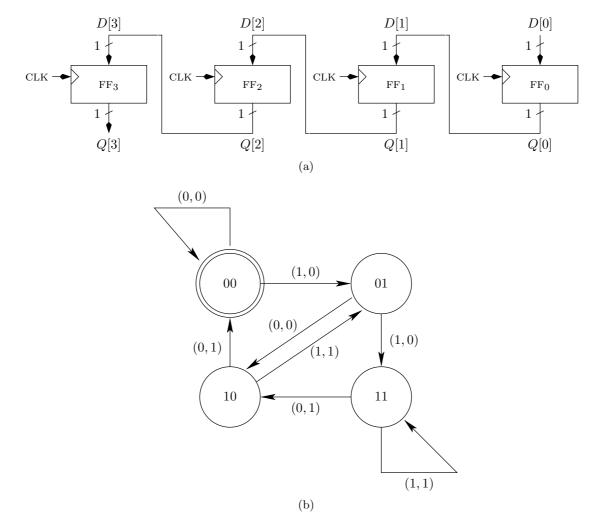

| 20 | Syn   | chronous Modules: Analysis and Synthesis 311 |

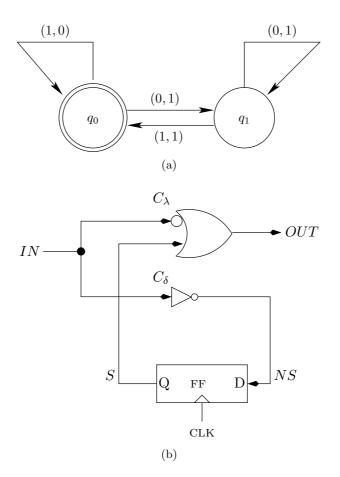

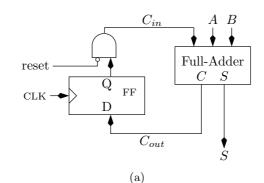

|    | 20.1  | Example: a two-state FSM                     |

|    | 20.2  | Sequential Adder                             |

|    |       | 20.2.1 Implementation                        |

|    |       | 20.2.2 Analysis                              |

|    | 20.3  | Initialization and the Corresponding FSM     |

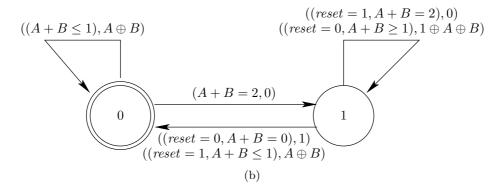

|    | 20.4  | Counter                                      |

|    |       | 20.4.1 Implementation                        |

|    |       | 20.4.2 Analysis                              |

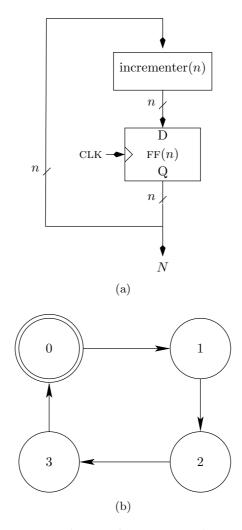

|    | 20.5  | Revisiting Shift Registers                   |

|    |       | 20.5.1 Analysis                              |

|    | 20.6  | Revisiting RAM                               |

|    |       | 20.6.1 Analysis                              |

|    |       | 20.6.2 Synthesis and Analysis                |

|    |       |                                              |

| IV | A     | Simplified DLX 325                           |

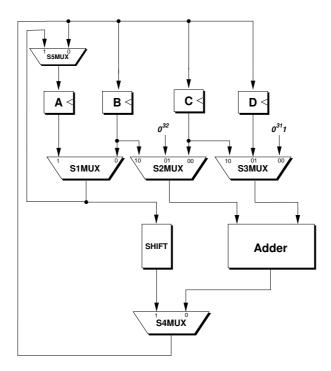

### 327 21 The ISA of a Simplified DLX 21.1 Why use abstractions? $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 32822 A Simplified DLX: Implementation 343 22.1.4 Shifter Environment $\ldots \ldots 347$

xiv

| CONTENTS     | XV  |

|--------------|-----|

| Bibliography | 365 |

| Index        | 367 |

### CONTENTS

$\mathbf{x}\mathbf{v}\mathbf{i}$

## List of Figures

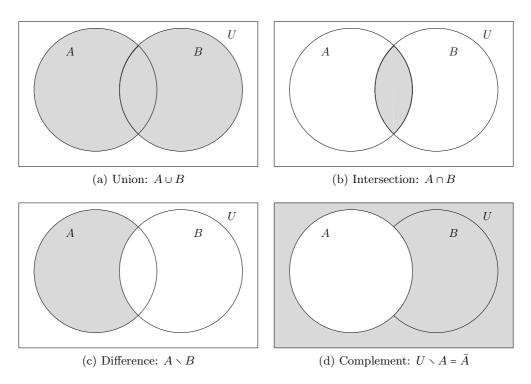

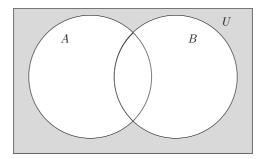

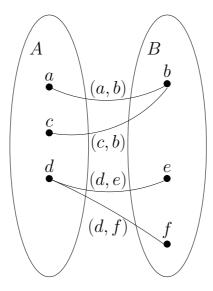

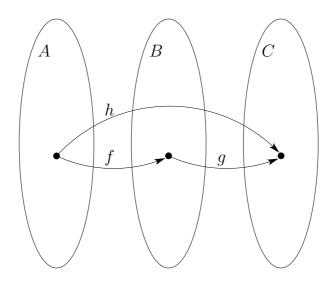

| $1.1 \\ 1.2 \\ 1.3 \\ 1.4$                                                                  | Venn diagrams8Venn diagram for $U \smallsetminus (A \cup B) = \overline{A} \cap \overline{B}$ 9A diagram of a binary relation $R \subseteq A \times B$ 10Composition of functions11                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $2.1 \\ 2.2$                                                                                | A counter example to "all the horses have the same color                                                                                                                                                                                                                                                                                                                                             |

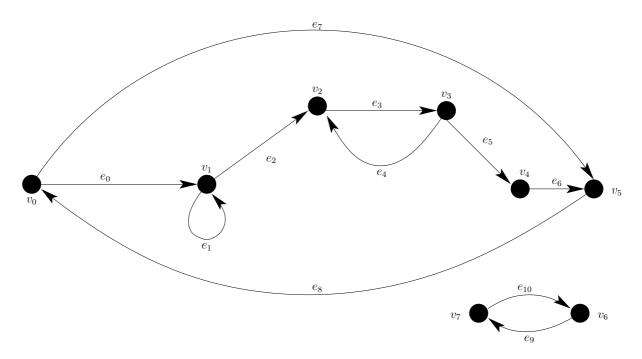

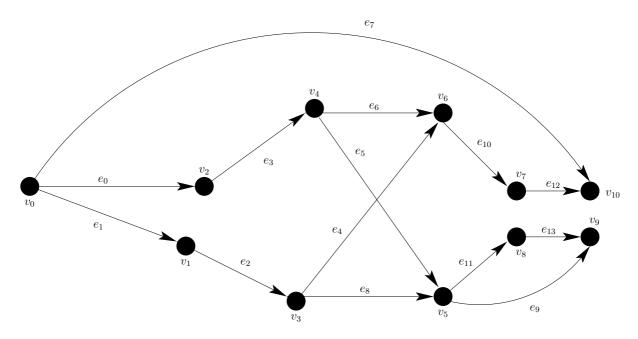

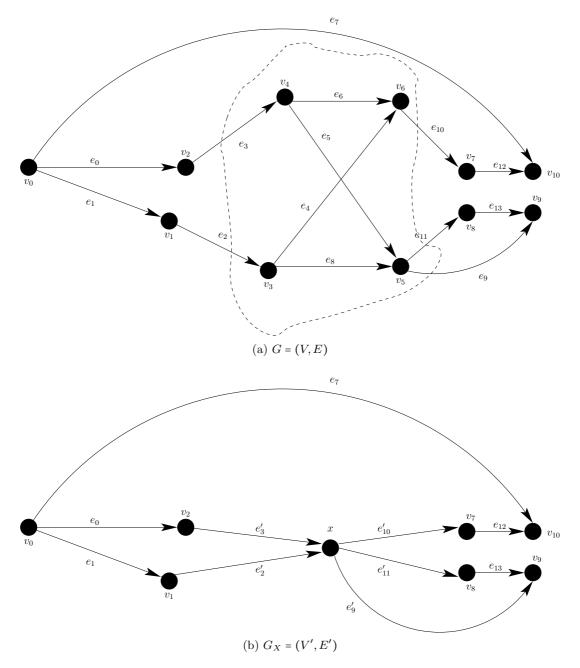

| $4.1 \\ 4.2 \\ 4.3$                                                                         | A directed graph $G = (V, E)$                                                                                                                                                                                                                                                                                                                                                                        |

| $6.1 \\ 6.2 \\ 6.3$                                                                         | An example of a parse tree74A parse tree of a Boolean formula86A substitution in Boolean formulas87                                                                                                                                                                                                                                                                                                  |

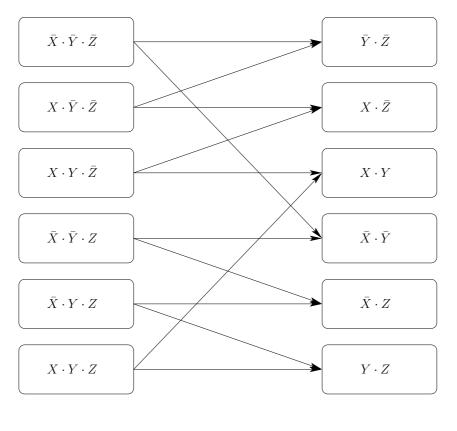

| 9.1<br>9.2                                                                                  | The implicants' graph                                                                                                                                                                                                                                                                                                                                                                                |

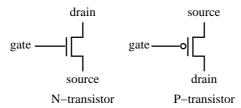

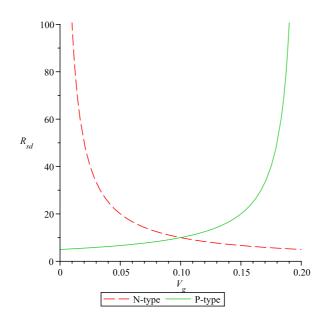

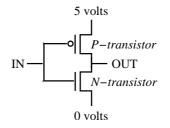

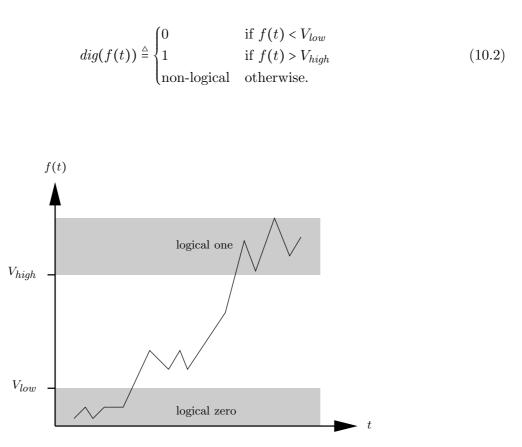

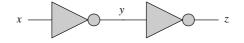

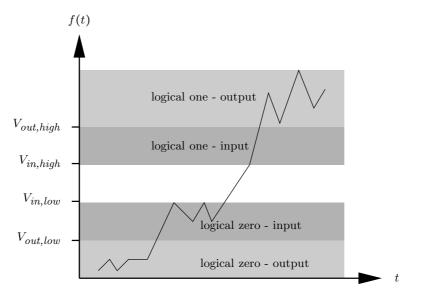

| $10.2 \\ 10.3 \\ 10.4 \\ 10.5$                                                              | Schematic symbols of an N-transistor and a P-transistor $\dots \dots \dots$                                                                                                                                                                                                                          |

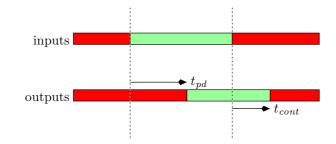

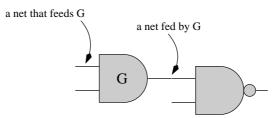

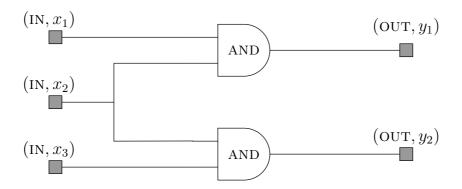

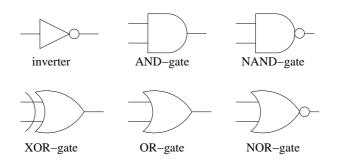

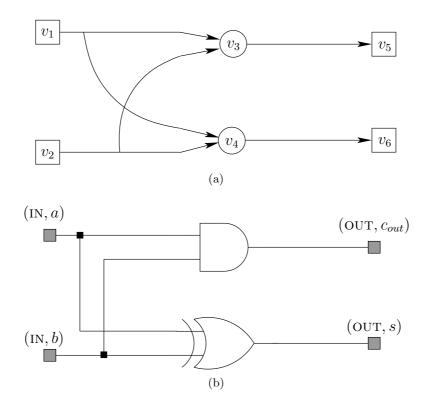

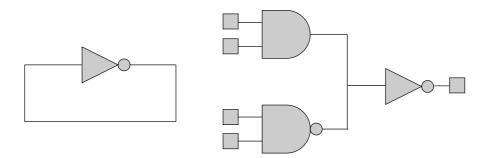

| $\begin{array}{c} 11.2 \\ 11.3 \\ 11.4 \\ 11.5 \\ 11.6 \\ 11.7 \\ 11.8 \\ 11.9 \end{array}$ | Propagation delay and contamination delay of a combinational gate.157An input gate and an output gate.158Three equivalent nets.159A terminal that is fed by a net and a terminal that feeds a net.160A combinational circuit.161Symbols of common gates.163A Half-Adder164Two examples of non-combinational circuits.164The merging operation on DAGs170OThe combinational circuit $C_{\varphi}$ 172 |

|                                                                                             | Two implementations of an OR-tree $(n)$ with $n = 4$ inputs                                                                                                                                                                                                                                                                                                                                          |

| 12.2 Two trees with six inputs                                                                                    |

|-------------------------------------------------------------------------------------------------------------------|

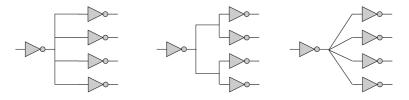

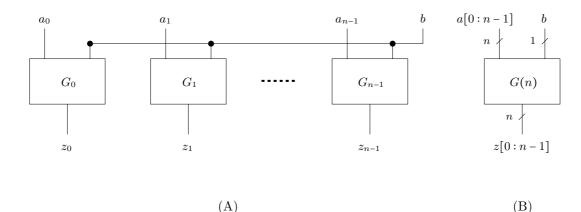

| 13.1 Vector notation: multiple instances of the same gate                                                         |

| 13.2 Vector notation: $b$ feeds all the gates                                                                     |

| 13.3 A recursive implementation of $DECODER(n)$                                                                   |

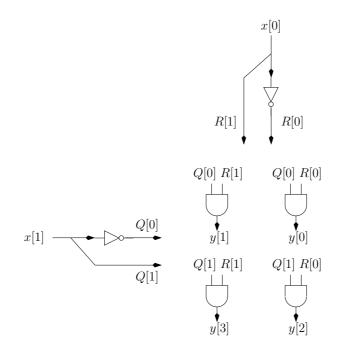

| 13.4 An implementation of $DECODER(2)$                                                                            |

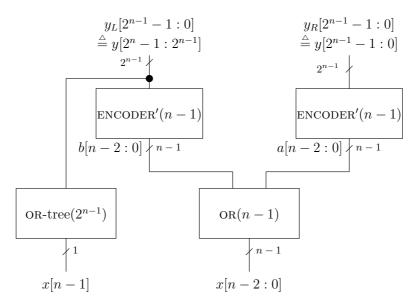

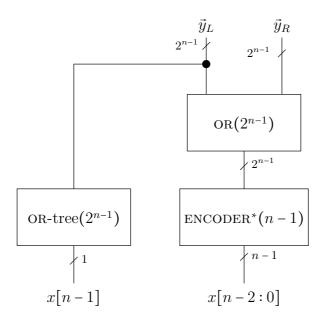

| 13.5 A recursive implementation of $ENCODER'(n)$                                                                  |

| 13.6 A recursive implementation of $\text{ENCODER}^*(n)$                                                          |

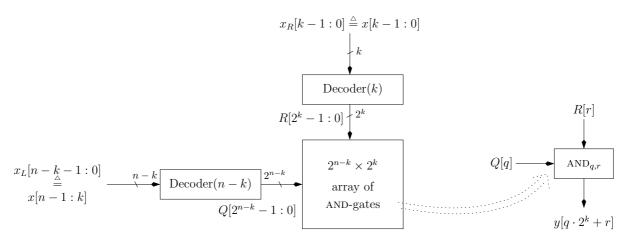

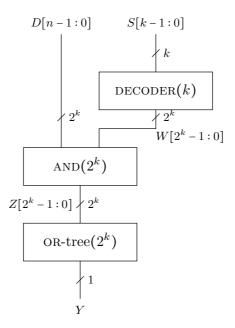

| 14.1 An $(n:1)$ -MUX based on a decoder $(n=2^k)$                                                                 |

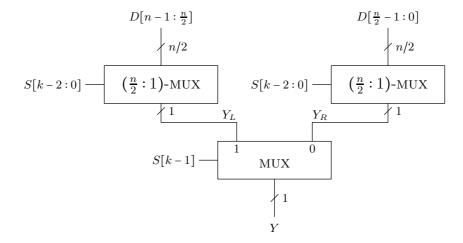

| 14.2 A recursive implementation of $(n:1)$ -MUX $(n=2^k)$                                                         |

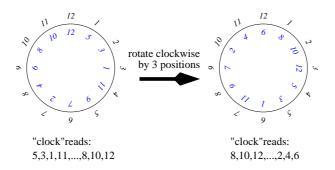

| 14.3 An example of a cyclic shift                                                                                 |

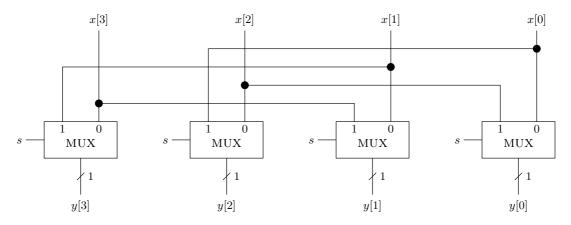

| 14.4 A row of multiplexers implement a $CLS(4,2)$                                                                 |

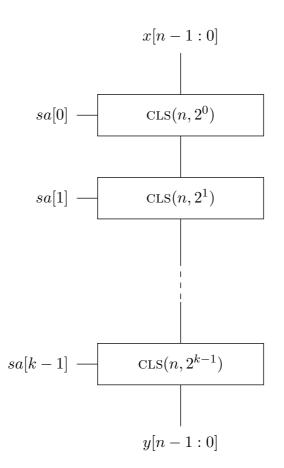

| 14.5 A BARREL-SHIFTER(n) built of k levels of $CLS(n, 2^i)$ $(n = 2^k)$                                           |

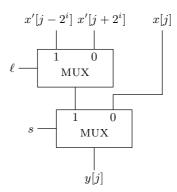

| 14.6 A bit-slice of an implementation of $LBS(n, 2^i)$                                                            |

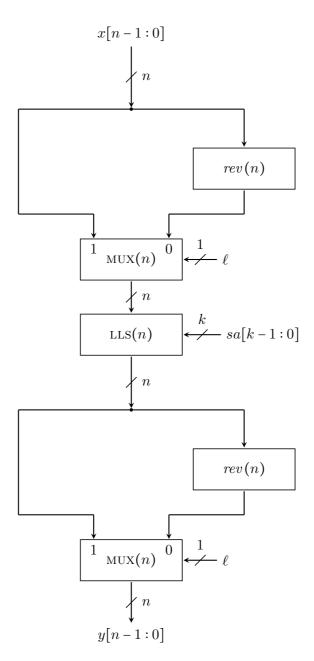

| 14.7 Reduction of right shift to left shift via reversing                                                         |

| 14.8 An implementation of a bidirectional logical shift L-SHIFT $(n)$ based on a logical left shifter LLS $(n)$ . |

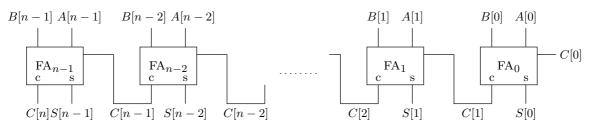

| 15.1 A Ripple Carry Adder $RCA(n)$                                                                                |

| 15.2 A recursive description of $RCA(n)$                                                                          |

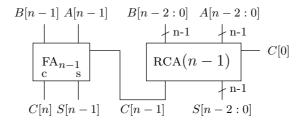

| 15.3 A Conditional Sum Adder $CSA(n)$                                                                             |

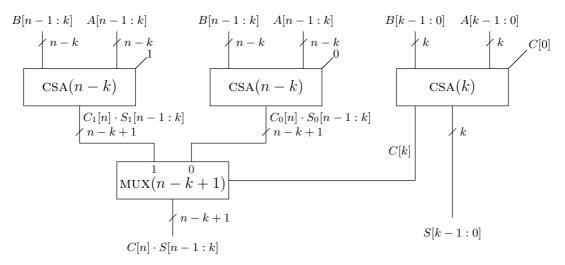

| 15.4 A Compound Adder COMP-ADDER $(n)$                                                                            |

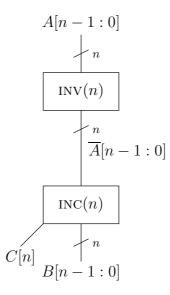

| 16.1 A (wrong) circuit for negating a value represented in two's complement                                       |

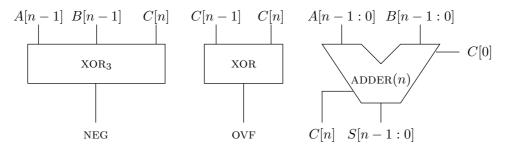

| 16.2 A two's complement adder S-ADDER $(n)$                                                                       |

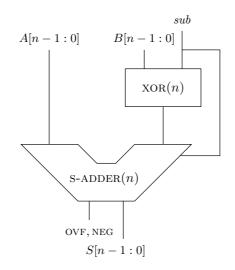

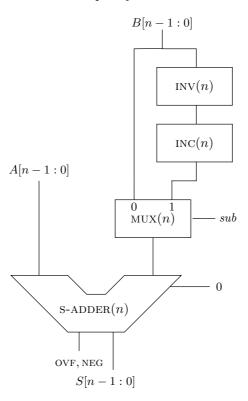

| 16.3 A two's-complement adder/subtractor ADD-SUB $(n)$                                                            |

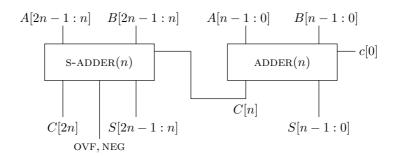

| 16.4 Concatenating an S-ADDER $(n)$ with an ADDER $(n)$                                                           |

| 16.5 A wrong implementation of ADD-SUB $(n)$                                                                      |

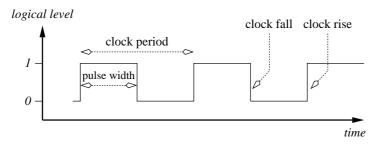

| 17.1 A clock signal                                                                                               |

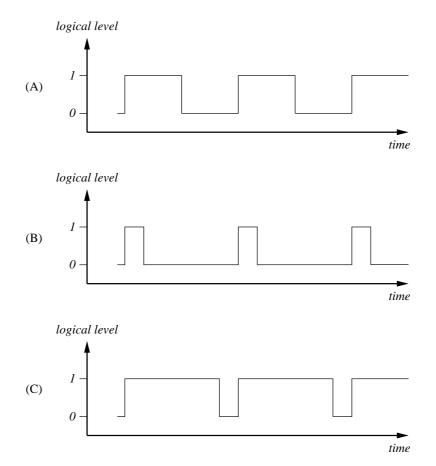

| 17.2 Clock signal examples                                                                                        |

| 17.3 A critical segment and an instability segment                                                                |

| 17.4 A simplified timing diagram of an edge-triggered flip-flop                                                   |

| 17.5 A schematic of an edge-triggered flip-flop                                                                   |

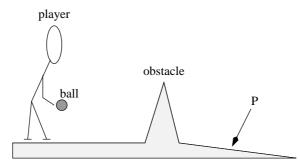

| 17.6 A player attempting to roll a ball so that it passes point $P. \ldots \ldots \ldots \ldots 268$              |

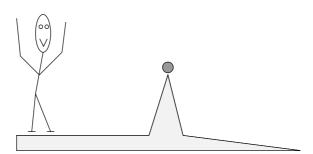

| 17.7 The event of metastability                                                                                   |

| 17.8 An arbiter based on a flip-flop without a critical segment                                                   |

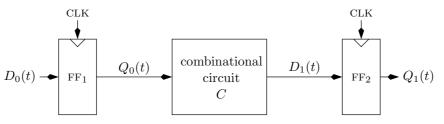

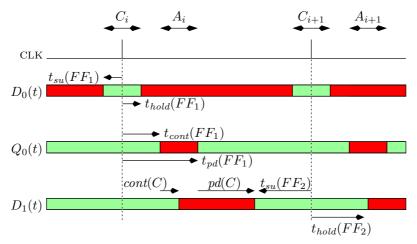

| 17.9 A circuit and its simplified timing analysis                                                                 |

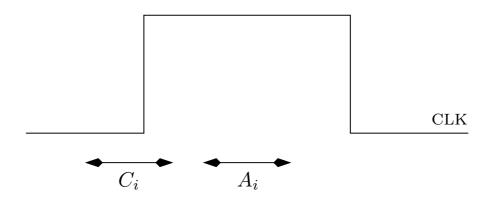

| 17.10 The simplified timing diagram in the case that $A_i \cap C_i \neq \emptyset$                                |

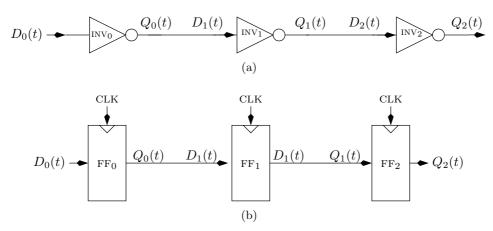

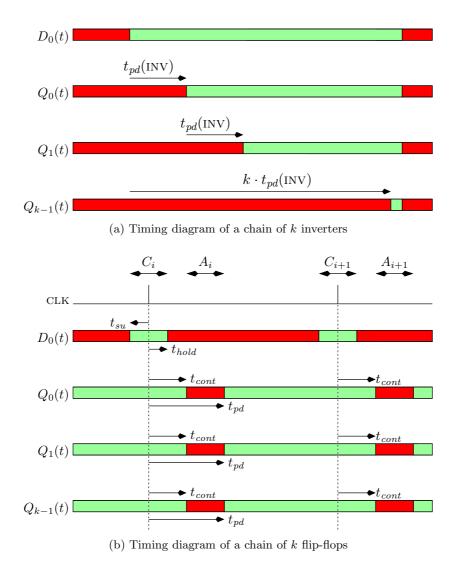

| 17.11A chain of $k$ inverters and a chain of $k$ flip-flops                                                       |

| 17.12Comparison of segments of instability in two chains                                                          |

| 17.13A timing diagram of a D-Latch                                                                                |

| 17.14A a schematic of a clock enabled flip-flop                                                                   |

| 17.15Implementations of a clock enabled flip-flop                                                                 |

| 17.10Slow and fast signals                                                                                        |

|                                                                                                                   |

| 18.1 A sequential XOR circuit                                                                                     |

| 18.2 | A 4-bit parallel load register                                                              |

|------|---------------------------------------------------------------------------------------------|

| 18.3 | A 4-bit shift register                                                                      |

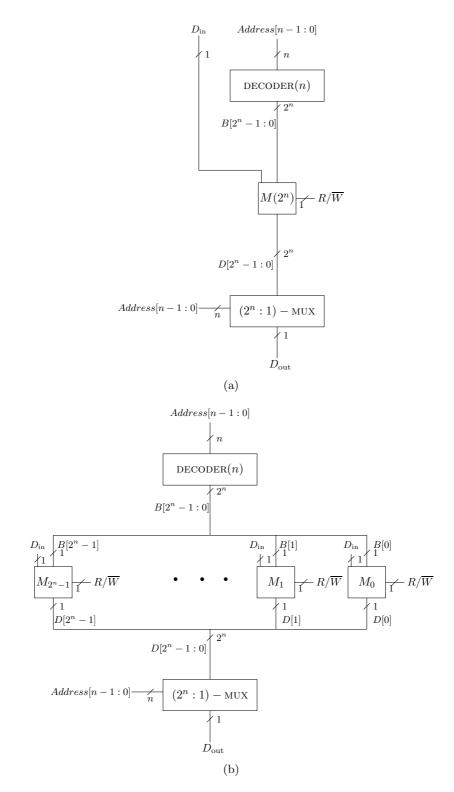

| 18.4 | A schematic of a $RAM(2^n)$                                                                 |

| 18.5 | A simplified implementation of a $RAM(2^n)$                                                 |

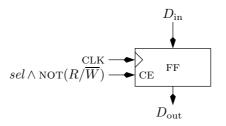

|      | An implementation of a memory cell                                                          |

| 18.7 | An implementation of a $ROM(2^n)$                                                           |

|      | Stripping away the flip-flops from a synchronous circuit                                    |

|      | A synchronous circuit in canonic form                                                       |

|      | A simple synchronous circuit                                                                |

|      | A synchronous circuit in canonic form with reset                                            |

|      | A state diagram of an FSM that counts (mod 4)                                               |

| 19.6 | An overly pessimistic timing analysis example for the canonic form. $\dots \dots \dots 302$ |

|      | A circuit                                                                                   |

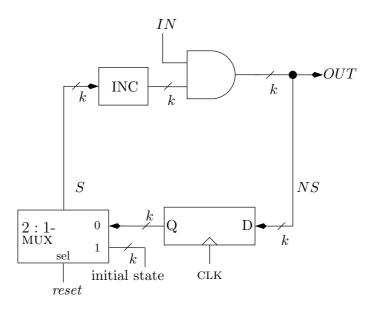

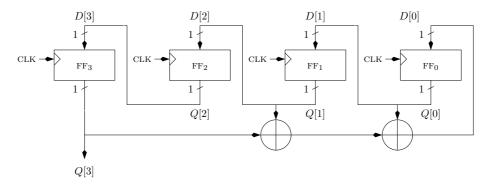

| 19.8 | An LFSR synchronous circuit with four FF's. The $\oplus$ denotes a XOR gate 310             |

|      | A two-state FSM and its implementation by a synchronous circuit                             |

|      | A sequential adder                                                                          |

|      | An <i>n</i> -bit counter                                                                    |

|      | A 4-bit shift-register, and an FSM of a 2-bit shift-register                                |

|      | A schematic of a $RAM(2^n)$ , and an FSM of a $RAM(2^1)$                                    |

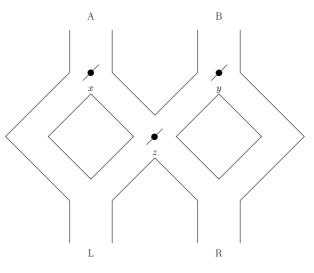

| 20.6 | A toy                                                                                       |

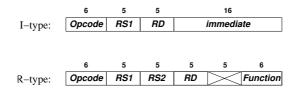

| 21.1 | Instruction formats of the simplified DLX                                                   |

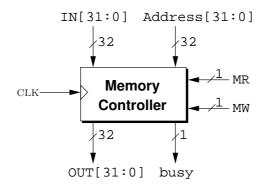

|      | The memory controller                                                                       |

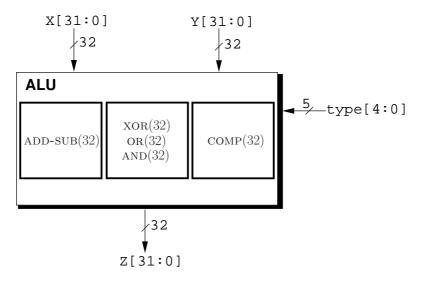

| 22.3 | A sketch of the ALU                                                                         |

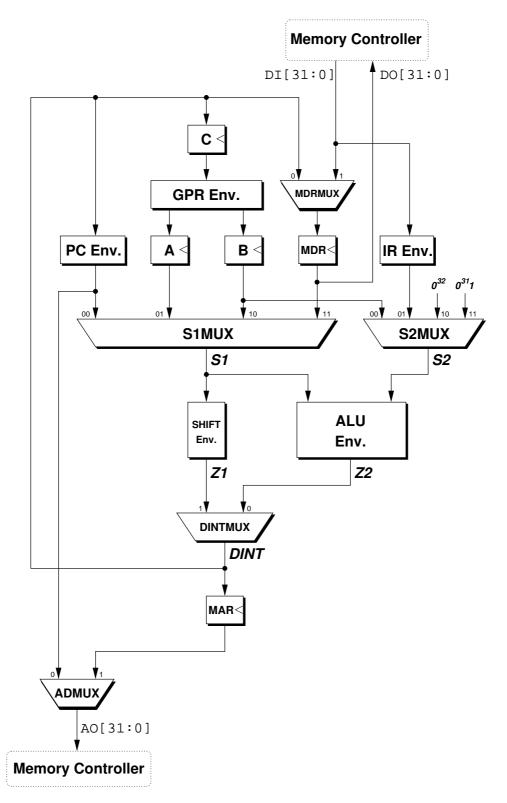

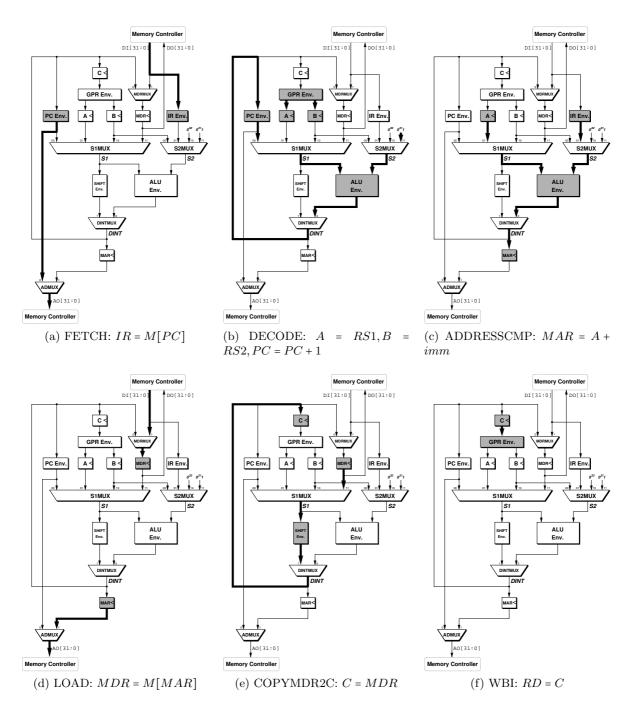

| 22.1 | Datapath of the simplified DLX machine                                                      |

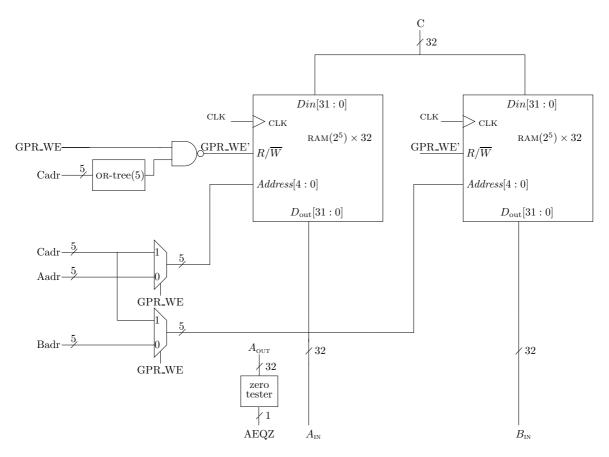

| 22.4 | An implementation of the GPR environment                                                    |

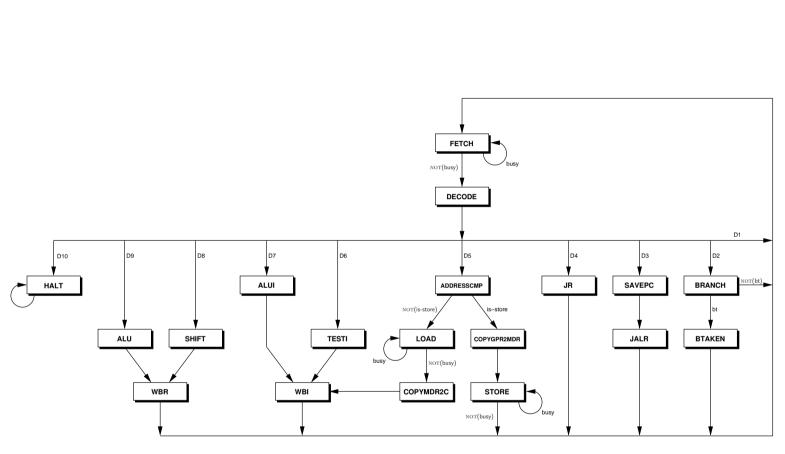

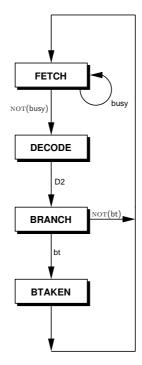

| 22.5 | Sketch of the state diagram of the control of the simplified DLX machine $\ldots$ 361       |

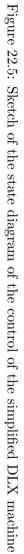

| 22.6 | The sequence of control states in the execution of the $lw$ instruction                     |

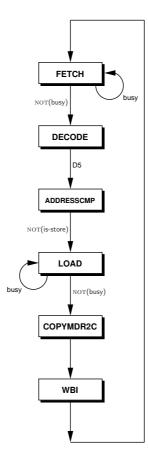

|      | Executing RTL instructions                                                                  |

| 22.8 | The sequence of control states in the execution of the 'beqz' instruction 364               |

| 22.9 | A simple data path                                                                          |

xix

### LIST OF FIGURES

## List of Tables

| 1.1  | Multiplication table                                                                                    |

|------|---------------------------------------------------------------------------------------------------------|

| 1.2  | Truth tables of four basic Boolean functions                                                            |

| 1.3  | Multiplication tables of three basic Boolean functions                                                  |

| 1.4  | Truth table the identity function $I: \{0, 1\} \rightarrow \{0, 1\}$                                    |

| 1.5  | The truth table of the 3-bit carry function                                                             |

| 1.6  | The truth tables of $AND(AND(a, b), c)$ and $AND(a, AND(b, c))$                                         |

| 6.1  | The tautology $X \lor \neg X$                                                                           |

| 6.2  | Two logically equivalent Boolean formulas                                                               |

| 6.3  | The implication connective                                                                              |

| 6.4  | The NAND and NOR connectives                                                                            |

| 6.5  | The equivalence connective                                                                              |

| 6.6  | The truth tables of the addition and the simplification tautologies                                     |

| 6.7  | The truth table of the "proof by contradiction" tautology                                               |

| 9.1  | The max Boolean function                                                                                |

| 9.2  | The NOT(max) Boolean function                                                                           |

| 9.3  | The truth table of $f: \{0,1\}^3 \rightarrow \{0,1\}$                                                   |

| 9.4  | The truth table of $f_1: \{0, 1\}^3 \to \{0, 1\}$                                                       |

| 9.5  | The truth table of $f_2: \{0, 1\}^3 \to \{0, 1\}$                                                       |

| 9.6  | The Karnaugh Map of $f_2: \{0,1\}^3 \to \{0,1\}$                                                        |

| 9.7  | The prime implicants of $f_2$                                                                           |

| 11.1 | Costs and delays of gates                                                                               |

| 16.1 | Comparison between representation of negative integers                                                  |

|      | Values of $C[n], C[n-1], [\vec{S}]$ , and z for various values of $[\vec{A}], [\vec{B}]$ and $C[0]$ 253 |

|      | Comparison of simulations of a parallel load register and a shift register 283                          |

| 20.1 | The truth table of $\lambda$                                                                            |

|      | I-type Instructions                                                                                     |

|      | R-type Instructions (in R-type instructions $IR[31:26] = 0^6$ )                                         |

|      | Register assignment for Example 21.8                                                                    |

|      | Conversion of C code to a DLX's machine code                                                            |

|      | Register assignment                                                                                     |

| 21.6 | Conversion of C code to a DLX's machine code                                                            |

| 22.1 | The type input and its corresponding function $f_{type}$          | 347 |

|------|-------------------------------------------------------------------|-----|

| 22.2 | Determining the transition from the Decode state                  | 353 |

| 22.3 | The RTL instructions and active control outputs per control state | 354 |

| 22.4 | Summary of the control outputs                                    | 355 |

## List of Algorithms

| 4.1  | Topological sorting                                                                                                 |

|------|---------------------------------------------------------------------------------------------------------------------|

| 4.2  | Longest path in a DAG 48                                                                                            |

| 4.3  | tree height                                                                                                         |

| 5.1  | Computing a binary representation                                                                                   |

| 5.2  | An LSB-to-MSB binary representation computation                                                                     |

| 6.1  | An algorithm for generating a Boolean formula from a parse tree                                                     |

| 6.2  | Evaluating the truth value of the Boolean formula                                                                   |

| 6.3  | Evaluating the truth value of the Boolean formula                                                                   |

| 6.4  | An algorithm for evaluating the De Morgan dual                                                                      |

| 6.5  | An algorithm for computing the negation normal form                                                                 |

| 9.1  | An algorithm for computing the set of prime implicants $\mathcal{I}(f)$                                             |

| 11.1 | A simulation algorithm for combinational circuits                                                                   |

|      | Weighted longest path in a DAG                                                                                      |

| 12.1 | Balanced-Tree $(n)$                                                                                                 |

| 16.1 | Computation of two's complement representation                                                                      |

| 19.1 | $\operatorname{FEAS}(C)$                                                                                            |

| 19.2 | $\operatorname{Min}-\Phi(C)  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                       |

| 19.3 | $\operatorname{SIM}(C, S_0, \{IN_i\}_{i=0}^{n-1})  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ |

|      |                                                                                                                     |

### LIST OF ALGORITHMS

xxiv

# Part I Preliminaries

### Chapter 1

### Sets and Functions

#### Contents

| 1.1 Sets                                          | 3         |

|---------------------------------------------------|-----------|

| 1.2 Relations and Functions                       | 10        |

| 1.3 Boolean Functions                             | <b>14</b> |

| 1.3.1 Truth Tables                                | 14        |

| 1.4 Commutative and Associative Binary Operations | 16        |

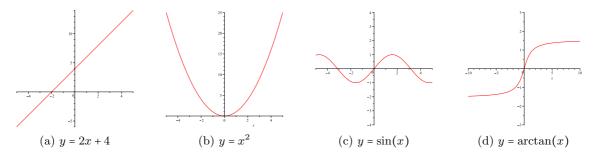

This chapter introduces two major notions: sets and functions. We are all familiar with real functions, for example, f(x) = 2x + 1 and  $g(x) = \sin(x)$ . Here the approach is somewhat different. The first difference is that we do not limit the discussion to the set of real numbers; instead, we consider arbitrary sets and are mostly interested in sets that contain only a finite number of elements. The second difference is that we do not define a "rule" for assigning a value for each x; instead, a function is simply a list of pairs (x, y), where y denotes the value of the function when the argument equals x. The definition of functions relies on the definitions of sets and relations over sets. That is why we need to define various operations over sets such as union, intersection, complement, and Cartesian product.

The focus of this book is Boolean functions. Boolean functions are a special family of functions. Their arguments and values are finite sequences of 0 and 1 (also called bits). In this chapter, we show how to represent a Boolean function by a truth table and multiplication tables. Other representations presented later in the book are Boolean formulas and combinational circuits.

#### **1.1** Sets

A set is a collection of objects. When we deal with sets, we usually have a universal set that contains all the possible objects. In this section, we denote the universal set by U.

The universal set need not be fixed. For example, when we consider real numbers, the universal set is the set of real numbers. Similarly, when we consider natural numbers, the universal set is the set of natural numbers. The universal set need not be comprised only of abstract objects such as numbers. For example, when we consider people, the universal set is the set of all people.

One way to denote a set is by listing the objects that belong to the set and delimiting them by curly brackets. For example, suppose the universe is the set of integers, and consider the set  $A = \{1, 5, 12\}$ . Then 1 is in A, but 2 is not in A. An object that belongs to a set is called an *element*. We denote the fact that 1 is in A by  $1 \in A$  and the fact that 2 is not in A by  $2 \notin A$ .

**Definition 1.1** Consider two sets A and B.

- 1. We say that A is a subset of B if every element in A is also an element in B. We denote that A is a subset of B by  $A \subseteq B$ .

- 2. We say that A equals B if the two sets consist of exactly the same elements, formally, if  $A \subseteq B$  and  $B \subseteq A$ . We denote that A and B are equal sets by A = B.

- 3. The union of A and B is the set C such that every element of C is an element of A or an element of B. We denote the union of A and B by  $A \cup B$ .

- 4. The intersection of A and B is the set C such that every element of C is an element of A and an element of B. We denote the intersection of A and B by  $A \cap B$ .

- 5. The difference A and B is the set C such that every element of C is an element of A and not an element of B. We denote the difference of A and B by  $A \setminus B$ .

We denote strict containment, i.e.,  $A \subseteq B$  and  $A \neq B$ , by  $A \subsetneq B$ . The *empty set* is a very important set (as important as the number zero).

**Definition 1.2** The empty set is the set that does not contain any element. It is usually denoted by  $\emptyset$ .

Sets are often specified by a condition or a property. This means that we are interested in all the objects in the universal set that satisfy a certain property. Let P denote a property. We denote the set of all elements that satisfy property P as follows:

$\{x \in U \mid x \text{ satisfies property } P\}.$

The preceding notation should be read as follows: the set of all elements x in the universal set U such that x satisfies property P.

Every set we consider is a subset of the universal set. This enables us to define the complement of a set as follows.

**Definition 1.3** The complement of a set A is the set  $U \setminus A$ . We denote the complement set of A by  $\overline{A}$ .

Given a set A, we can consider the set of all its subsets.

**Definition 1.4** The power set of a set A is the set of all the subsets of A. The power set of A is denoted by P(A) or  $2^A$ .

We can pair elements together to obtain ordered pairs.

**Definition 1.5** Two objects (possibly equal) with an order (i.e., the first object and the second object) are called an ordered pair. We denote an ordered pair by (a,b). This notation means that a is the first object in the pair and b is the second object in the pair.

Consider two ordered pairs (a,b) and (a',b'). We say that (a,b) = (a',b') if a = a' and b = b'.

#### 1.1. SETS

We usually refer to the first object in an ordered pair as the first *coordinate*. The second object is referred to as the second coordinate.

An important method to build large sets from smaller ones is by the *Cartesian product*.

Definition 1.6 The Cartesian product of the sets A and B is the set

$$A \times B \stackrel{\scriptscriptstyle \Delta}{=} \{(a, b) \mid a \in A \text{ and } b \in B\}.$$

Every element in a Cartesian product is an ordered pair. Thus the Cartesian product  $A \times B$  is simply the set of ordered pairs (a, b) such that the first coordinate is in A and the second coordinate is in B. The Cartesian product  $A \times A$  is denoted by  $A^2$ .

The definition of ordered pairs is extended to tuples as follows.

**Definition 1.7** A k-tuple is a set of k objects with an order. This means that a k-tuple has k coordinates numbered  $\{1, \ldots, k\}$ . For each coordinate i, there is an object in the ith coordinate.

An ordered pair is a 2-tuple. A k-tuple is denoted by  $(x_1, \ldots, x_k)$ , where the element in the *i*th coordinate is  $x_i$ . Tuples are compared in each coordinate, thus,  $(x_1, \ldots, x_k) = (x'_1, \ldots, x'_k)$  if and only if  $x_i = x'_i$  for every  $i \in \{1, \ldots, n\}$ .

We also extend the definition of Cartesian products to products of k sets as follows.

**Definition 1.8** The Cartesian product of the sets  $A_1, A_2, \ldots, A_k$  is the set

$$A_1 \times A_2 \times \cdots \times A_k \stackrel{\scriptscriptstyle \Delta}{=} \{(a_1, \ldots, a_k) \mid a_i \in A_i \text{ for every } 1 \le i \le k\}.$$

The Cartesian product of k copies of A is denoted by  $A^k$ .

#### Examples

0<sup>\*</sup>. **Russell's paradox.** A formal axiomatic development of set theory is a branch of logic called *axiomatic set theory*. This branch developed in response to paradoxes in set theory. One of the most famous paradoxes was discovered by Bertrand Russell in 1901.

Suppose we do not restrict ourselves to a subset of a universal set. Consider the set Z defined by

$$Z \stackrel{\scriptscriptstyle \Delta}{=} \{ x \mid x \notin x \},\$$

namely, an object x is in Z if and if only it does not contain itself as an element.

Russell's paradox is obtained as follows. Is  $Z \in Z$ ? If  $Z \in Z$ , then because every element  $x \in Z$  satisfies  $x \notin x$ , we conclude that  $Z \notin Z$ —a contradiction. So we are left with the complementary option that  $Z \notin Z$ . But if  $Z \notin Z$ , then Z satisfies the only condition for being a member of Z. Thus  $Z \in Z$ —again, a contradiction.

- 1. Examples of sets: (i)  $A \stackrel{\scriptscriptstyle \triangle}{=} \{1, 2, 4, 8\}$ , the universal set is the set of numbers; (ii)  $B \stackrel{\scriptscriptstyle \triangle}{=} \{\text{pencil}, \text{pen}, \text{eraser}\}$ , the universal set is the set of "the things that we have in our pencil case."

- 2. Examples of subsets of  $A \stackrel{\scriptscriptstyle \triangle}{=} \{1, 2, 4, 8\}$  and  $B \stackrel{\scriptscriptstyle \triangle}{=} \{\text{pencil}, \text{pen}, \text{eraser}\}$ : (i)  $\{1, 2, 4, 8\} \subseteq A$ ; (ii)  $\{1, 2, 4\} \subseteq A$ ; (iii)  $\{1, 2, 4\} \subseteq A$ ; (iv)  $\{1, 2\} \subseteq A$ ; (v)  $\{1\} \subseteq A$ ; (vi)  $\emptyset \subseteq A$ ; (vii)  $\{\text{pen}\} \subseteq B$ .

- 3. Examples of equal sets. Let  $A \triangleq \{1, 2, 4, 8\}$  and  $B \triangleq \{\text{pencil}, \text{pen}, \text{eraser}\}$ : (i) order and repetitions do not affect the set, e.g.,  $\{1, 1, 1\} = \{1\}$  and  $\{1, 2\} = \{2, 1\}$ ; (ii)  $\{2, 4, 8, 1, 1, 2\} = A$ ; (iii)  $\{1, 2, 44, 8\} \neq A$ ; (iv)  $A \neq B$ .